Flip-flop ir termins, kas attiecas uz digitālo elektroniku, un tas ir elektronisks komponents, ko izmanto, lai uzglabātu vienu informācijas bitu.

Flip Flop diagrammiskais attēlojums

- Tā kā Flip Flop ir secīga ķēde, tā ievade ir balstīta uz diviem parametriem, viens ir pašreizējā ieeja un otrs ir iepriekšējā stāvokļa izeja.

- Tam ir divas izejas, abas viena otru papildina.

- Tas var būt vienā no diviem stabiliem stāvokļiem — 0 vai 1.

Flip Flop pamata diagramma

Kas ir T Flip Flop?

- T flip flop vai, precīzāk, ir pazīstams kā Toggle Flip Flop, jo tas var pārslēgt savu izvadi atkarībā no ievades.

- T šeit apzīmē Pārslēgt .

- Pārslēgt būtībā norāda, ka bits tiks pagriezts, t.i., vai nu no 1 uz 0 vai no 0 uz 1.

- Šeit tiek piegādāts pulksteņa impulss, lai darbinātu šo flopu, tāpēc tas ir pulksteņa flip-flop.

T Flip Flop uzbūve

Mēs varam izveidot T flip trīs veidos, proti:

- Izmantojot SR Flip Flops.

- Izmantojot D Flip Flops.

- Izmantojot JK Flip Flops

Veidi, kā izveidot T Flip Flop

Apskatīsim T Flip Flop konstrukciju, izmantojot SR Flip Flops, kam nepieciešami 2 AND vārti un 2 NOR vārti, kā parādīts zemāk:

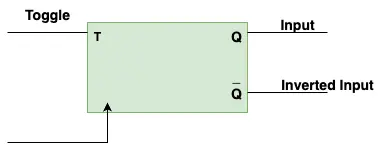

T Flip Flop pamata blokshēma

Šeit blokshēma satur pārslēgšanas un pulksteņa ieejas, Q un Q ir papildinātās ieejas.

T Flip Flop darbība

1. gadījums : Teiksim, T = 0 un pulksteņa impulss ir augsts t.i., 1, tad abu, UN vārti 1, UN vārti 2 izvade būs 0 , vārti 3 izlaide būs J un līdzīgi vārti 4 izlaide būs Q' tāpēc abas Q un Q vērtības ir tādas pašas kā to iepriekšējā vērtība, kas nozīmē Aiztures stāvoklis .

2. gadījums : Teiksim, T=1 , tad būs abu UN vārtu 1 izvade (T * pulkstenis * Q) , un tā kā T un pulkstenis abi ir 1, tad UN vārtu 1 izvade būs J , un līdzīgi būs UN vārtu 2 izvade (T * pulkstenis * Q’) i., Q' . Tagad vārtu 3 izeja būs (Q'+Q)' un pieņemsim, ka Q ir nulle, tad vārtu 3 izeja būs (0+Q)' kas nozīmē Q' un līdzīgi vārtu 4 izeja būs (Q+Q’)” un tā kā Q' ir nulle, tātad 4. vārtu izeja būs Q', kas nozīmē 0 jo Q' ir nulle. Tādējādi šajā gadījumā mēs varam teikt, ka izvade pārslēdzas, jo T=1 .

T Flip Flop patiesības tabula

- Šeit T ir pārslēgšanas ievade, Q ir pašreizējā stāvokļa ievade, Qt+1 ir nākamā stāvokļa izvade.

- No šejienes mēs varam redzēt, ka ikreiz, kad pārslēgšana (T) ir 0, nākamā stāvokļa izvade (Qt+1) ir tāda pati kā pašreizējā stāvokļa ieeja (Q).

- Ikreiz, kad pārslēgšanās (T) ir 1, nākamā stāvokļa izvade (Qt+1) būs pašreizējā stāvokļa ievades (Q) papildinājums, kas nozīmē, ka tā tiek pārslēgta.

Raksturīgais vienādojums

- Raksturīgais vienādojums mums parāda, kāds būs nākamais flip flopa stāvoklis pašreizējā stāvokļa izteiksmē.

- Lai iegūtu raksturīgo vienādojumu, tiek izveidots K-Map, kas tiks parādīts šādi:

- Ja mēs atrisināsim iepriekš minēto K-Map, tad raksturīgais vienādojums būs Q(n+1) = TQn’ + T’Qn = T XOR Qn

Uzbudinājuma tabula

Uzbudinājuma tabula būtībā stāsta par ierosmi, kas nepieciešama flip flopam, lai pārietu no pašreizējā stāvokļa uz nākamo stāvokli.

- Šeit, kad T ir 0, Qt+1 ir tāds pats kā ievade Q.

- Un vienmēr, kad T ir 1, Qt+1 papildina ievadi Q.

T Flip Flop pielietojumi

Digitālajā sistēmā ir daudz T Flip Flop lietojumu, kas ir uzskaitīti zemāk:

- Skaitītāji : T Flip Flops, ko izmanto skaitītājos. Skaitītāji uzskaita notikumu skaitu, kas notiek digitālajā sistēmā.

- Datu glabāšana : T Flip Flops, ko izmanto, lai izveidotu atmiņu, ko izmanto datu glabāšanai, kad barošana ir izslēgta.

- Sinhronās loģiskās shēmas : T flip-flops var izmantot, lai ieviestu sinhronās loģiskās shēmas, kas ir shēmas, kas veic darbības ar bināriem datiem, pamatojoties uz pulksteņa signālu. Sinhronizējot loģiskās shēmas darbības ar pulksteņa signālu, izmantojot T flip-flops, ķēdes darbību var padarīt paredzamu un uzticamu.

- Frekvences dalījums : To izmanto, lai dalītu pulksteņa signāla frekvenci ar 2. Flip-flop pārslēgs savu izvadi ikreiz, kad pulksteņa signāls pāriet no augsta uz zemu vai zemu uz augstu, tādējādi dalot pulksteņa frekvenci ar 2.

- Maiņu reģistri : T flip-flops var izmantot maiņu reģistros, kurus izmanto, lai pārvietotu bināros datus vienā virzienā.

Secinājums

Šajā rakstā mēs sākam no flip flops pamatiem, kas patiesībā ir flip flops, un pēc tam mēs apspriedām T Flip Flops, trīs divus veidus, kā mēs varam izveidot T Flip Flops, tā ir pamata blokshēma, T Flip Flop darbība. , tā ir patiesības tabula, raksturīgo vienādojums, kā arī ierosmes tabula, un beigās mēs apspriedām T Flip Flops lietojumus.